测试设备:

(1)信号发生器(主要指标是带宽、有调幅功能、能自动或手动扫描、扫描点上的留驻时间可设定、信号的幅度能自动控制等);

(2)功率放大器(要求在1m法、3m法或10m法①的情况下,达到标准规定的场强。对于小产品,也可以采用lm法进行测试,但当lm法和3m法的测试结果有出入时,以3m法为准);

(3)天线(在不同的频段下使用双锥和对数周期天线);

(4)场强测试探头;

(5)场强测试与记录设备。在基本仪器的基础上再增加一些诸如功率计、计算机(包括专用的控制软件)、场强探头的自动行走机构等,可构成一个完整的自动测试系统;

(6)电波暗室,为了保证测试结果的可比性和重复性,要对测试场地的均匀性进行校验;(7)横向电磁波室(TEM小室)、带状线天线、平行板天线;

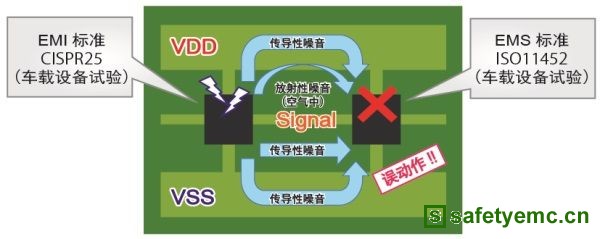

辐射电磁场抗扰度测试方法

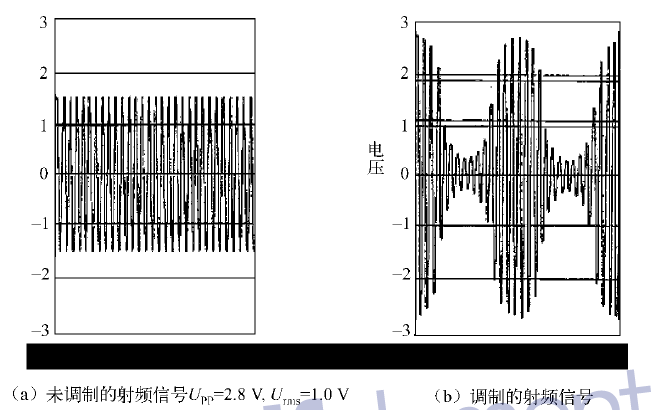

测试时要用 1KHz正弦波进行幅度调制, 调制深度为 80%, 参见下图 (在早期的测试标准中不需要调制)。将来有可能再增加一项键控调频 (欧共体标准已采用), 调制频率为 200Hz, 占空比为 1:1。

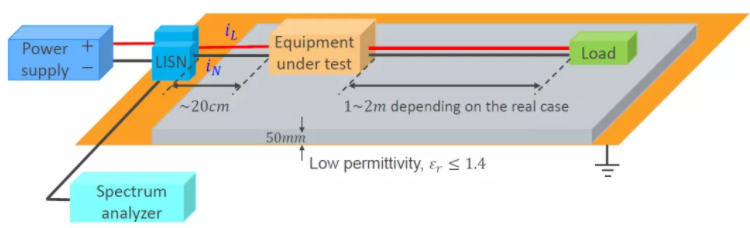

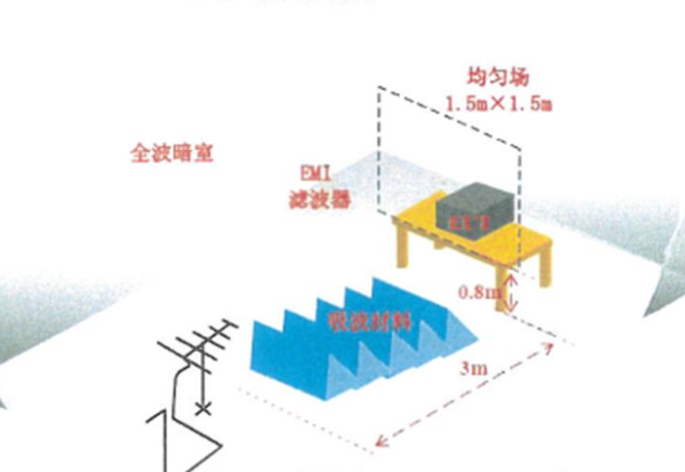

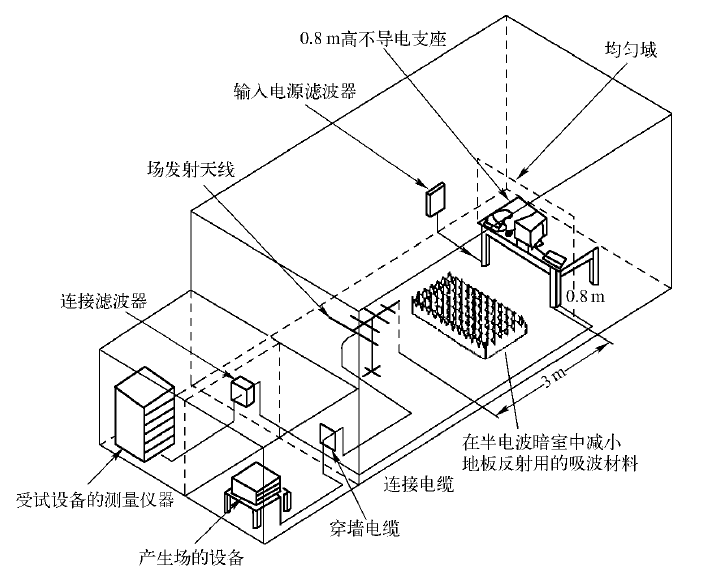

信号发生器的输出电压波形测试在电波暗室中进行(如下图),用监视器监视试品的工作情况 (或从试品引出可以说明试品工作状态的信号至测定室,由专门仪器予以判定)。暗室内有天线 (包括天线的升降塔)、转台、试品及监视器。工作人员、测定试品性能的仪器、信号发生器、功率计和计算机等设备在测定室里。高频功率放大器则放在功放室里。测试中,对试品的布线非常讲究,应记录在案,以便必要时重现测试结果。

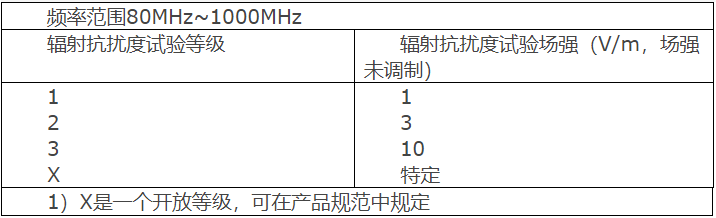

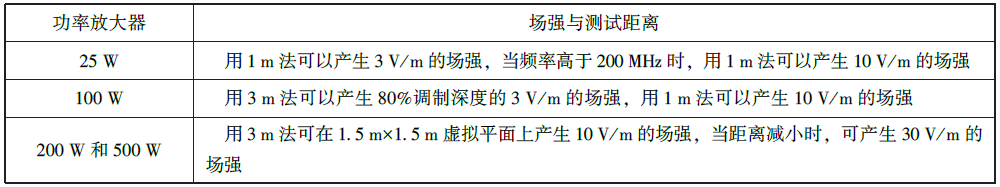

射频辐射电磁场抗扰度测试装置场强、测试距离与功率放大器的关系见表:

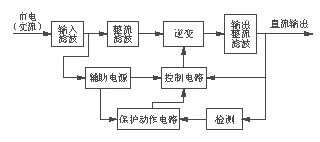

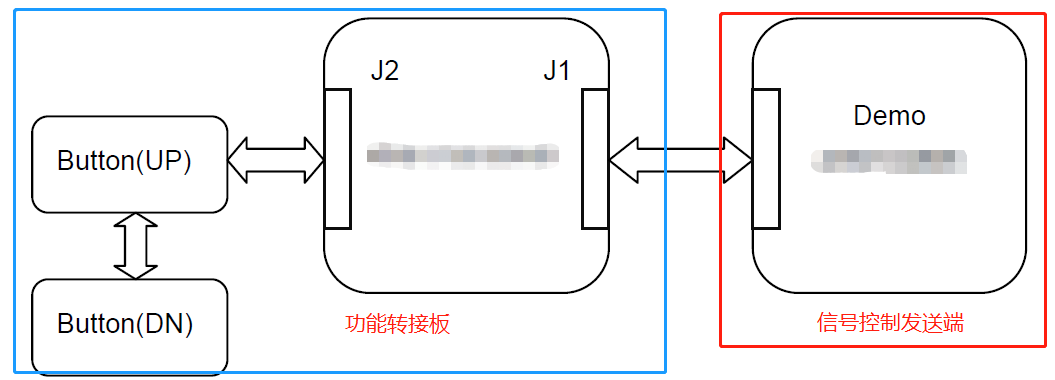

遇到的问题:公司开发了一款功能转接板,该功能转接板在正常运行过程中,转接板接收到控制系统的发出的指令后,会有扬声器发声。其功能框图如下图所示:

功能测试框图

功能介绍:该系统分为两部分,第一部分是最右侧的信号控制发送端,第二部分是左侧的功能转接板,功能转接板上有按钮动作开关以及扬声器发声驱动模块。产品正常运行过程中转接板接收到控制系统的发出的指令后,会有扬声器发声。

异常问题点:产品在做辐射抗扰度测试(RS测试)的过程中发现,发现即使控制系统不给转接板发信号,转接板上的扬声器也会发出声音,并且重复试验后发现干扰在400MHz~600MHz宽频带范围内均有发生。

现场捣鼓一下,毕竟实验室约一次不容易。。。现场拆开产品的结构,“这TM都谁准备的样机,线就这样一坨,绕线跟印度学的吗”,硬件工程师发自灵魂的追问。肯定是这个问题,待我整理整理线束重测一遍。然并卵用,再次测试,干扰音问题没有改善。再再次测试,还是没有改善。我和我的小伙伴陷入了沉默...

回去以后,和部门同事们一起分析原理图和Layout,在原有硬件基础上针对性的提出如下几个可行的方案。大概过了一周以后,终于又约到了实验室。开始愉快的玩耍。。。

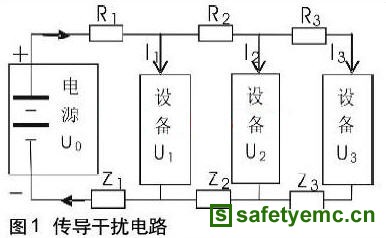

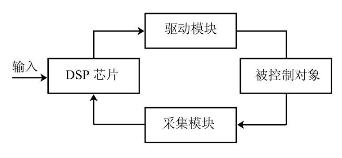

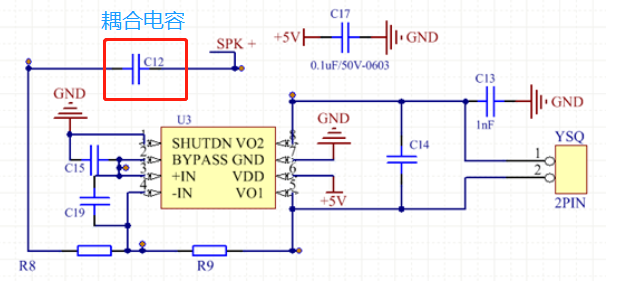

分析原理图部分,整个电路分为前级信号产生和后级驱动两部分,两部分通过一个耦合电容相连。

验证是前级还是后级耦合进入的干扰,这是方向性的问题,需要去首先确定。首先音频信号经过信号控制发声端发送到功能转接板,功能转接板接收信号后发出驱动信号给扬声器驱动电路。因此首先去排查是前级单片机收到干扰导致异常发生还是后端扬声器驱动电路导致异常发生。分析原理图可以知道C12是链接前后级的耦合电容,因此先去掉C12进行测试。

图 1 后级电路

测试结果:发现去掉C12和不去掉都会干扰音产生,这说明RS主要是通过C12之后的后级电路进去的。方向定了,整改的范围也就缩小了。针对后级电路的存在的问题做了如下整理和相应改善措施:

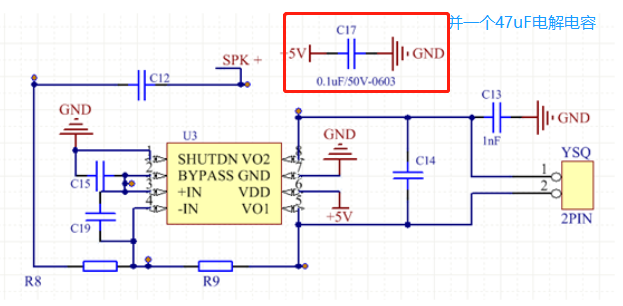

问题及改善措施1:该芯片是扬声器功率驱动芯片,扬声器在工作时,最大电流可以达到最大值400mA,分析这部分电路不难看出,驱动芯片电源端仅放置一颗0603封装、容值为100nF的瓷片电容C17。该部分电路存在风险。建议在PCB板上U3电源输入口增加一个47uF的电解电容,改善重负载时芯片电源端的瞬态响应。如下图所示:

测试结果:有一定改善,但是不明显。

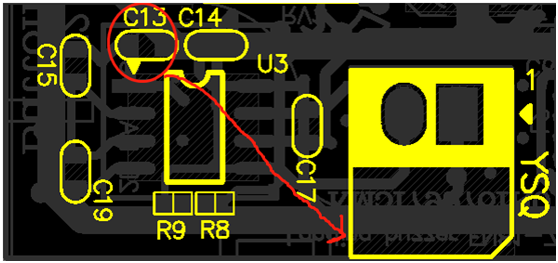

问题及改善措施2:针对图1中扬声器功率驱动部分电路专门查看了PCB Layout的布局,发现扬声器YSQ的去耦电容C13离去耦目标扬声器较远,效果上达不到设计目标。因此在PCB上做如下修改,将C13电容手动焊接到靠近扬声器位置。

测试结果:改善效果较措施1好一些,但是不完全解决干扰问题。

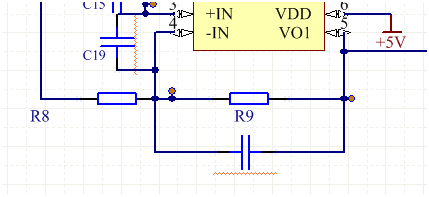

问题及改善措施3:系统有效信号是3kHz,干扰信号频段在400MHz以上,有效信号与干扰之间的频段区分明显,因此容易设计滤波器去滤除干扰。查看电路,考虑在信号输出到扬声器的这段路径中加低通滤波器,可以在R9上并联一个33pF的电容,与R9组成截止频率为530kHz的低通滤波器,如下图所示:

测试结果:多个样机反复测试,干扰噪音消失。

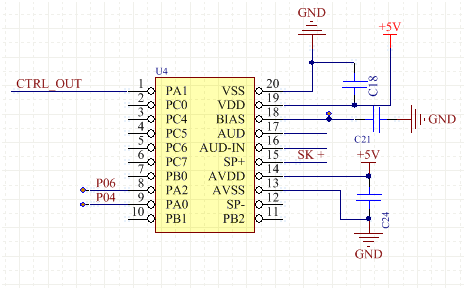

其他改善措施:虽然最终我们找到了解决问题的方法,但是同时也对电路上的一些其他部分做了改善,如原理图前段信号部分,发现其中一个芯片原理图设计存在风险点:所有未使用引脚均悬空,未做任何端接处理,如下图。这样会更容易引起干扰,在原板子上将所有悬空引脚连接后接4.7k电阻接地处理。

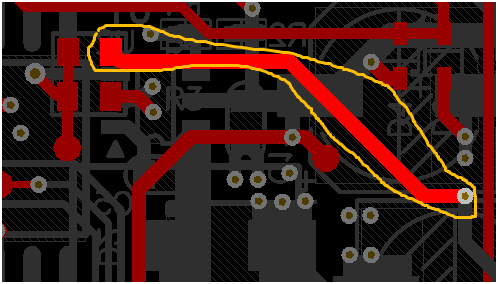

原理图中诸多芯片供电都是用的Buck芯片转换来的5V电源,开关电源是强EMI辐射源也是容易受干扰的部分,尤其是环路部分处理不好极其容易受干扰。查看PCB Layout发现5V反馈网络从输出到反馈电阻的距离较远,如下图,此网络为敏感部分,采取电源方案更换,将Buck芯片部分的电路去掉,换用线性稳压器方案。

通过这个实际案例,也吸取了一些教训:

1.原理图设计时候要参照测试标准做相应的防护设计,设计要自行分析,切记盲目相信公司成熟电路,以及datasheets上的推荐电路,吃亏上当不是一次两次了;

2.搞原理图的要和搞Layout的沟通好,尤其是关键器件的布局,要当面沟通,并在原理图中做好标识;

3.设计评审时候拉着工艺、结构等同事多角度评审,最近估计还要拉上采购,因为你设计好的东西可能买不到物料了;

4.测试结果应具有可重复性,可重复性在一定程度上体现测试系统及测试方法的可靠性;